Within modern aviation, aircraft communication networks’ effectiveness and dependability are crucial.

Avionics Full-Duplex Switched Ethernet (AFDX) is a revolutionary development in this field.

As it provides customers with the Ethernet network connectivity and bandwidth benefits they have been waiting years to utilize.

AFDX is becoming more and more popular throughout the avionics business and even in some unexpected non-avionics domains.

While military combat aircraft are adopting Fibre Channel, several major commercial aircraft, like the Airbus A380, are scheduled to adopt AFDX (ARINC 664).

The development and importance of AFDX in aircraft systems are examined in this blog. We’ll look at its technical details, historical background, and salient features.

We will also go over the benefits of AFDX for unmanned aerial vehicles (UAVs), military aircraft, and commercial aircraft, as well as how it works and its data flow processes.

We hope to show in this overview why AFDX is essential to the advancement of aviation technology.

What is AFDX?

AFDX, also known as ARINC 664, is a data network designed for safety-critical applications that uses dedicated bandwidth and deterministic quality of service (QoS).

It is patented by the global airplane manufacturer Airbus. Airbus has registered the trademark AFDX as a global trademark.

Using commercial off-the-shelf (COTS) components, the AFDX data network is built on Ethernet technology.

The AFDX data network is a particular application of ARINC Specification 664 Part 7, which outlines the way that commercially available networking components would be utilized for next-generation aircraft data networks (ADN).

Parts 1 and 2 of this specification describe a profiled version of an IEEE 802.3 network.

History of AFDX

The 1977-developed ARINC 429 standard is widely used in commercial aviation for applications requiring high levels of safety.

A unidirectional bus with a single transmitter and up to twenty receivers is used by ARINC 429.

32 bits are transmitted across a twisted pair cable as part of a data word using the bipolar return-to-zero modulation.

There are two transmission speeds: 12.5 kbit/s for low speed and 100 kbit/s for high speed.

As ARINC 429 relies on a point-to-point link for communication, a substantial quantity of wiring is needed, adding to the system’s weight.

Boeing also introduced ARINC 629 for the 777, which allowed for a maximum of 120 data terminals and faster data rates of up to 2 Mbit/s.

Although this ADN doesn’t require a bus controller to function, the network design is more reliable.

The disadvantage is that it needs specialized hardware, which raises the aircraft’s price considerably.

As a result, the ARINC 629 standard was not widely accepted by other manufacturers.

The next generation of airplane data networks is called AFDX.

Commercial off-the-shelf gear can save money and development time by being built on IEEE 802.3 committee standards, also known as Ethernet.

Part 7 of the ARINC Specification 664 defines AFDX as one implementation of deterministic Ethernet.

Airbus Industries created AFDX for the A380, initially to handle real-time problems for the development of flight-by-wire systems.

A cascaded star topology can be created by bridging many switches together.

This kind of network can drastically cut down on wire runs and, consequently, aircraft weight. AFDX can also offer dual-link redundancy and high-quality service.

With avionics and systems provided by Rockwell Collins, the Airbus A350 leverages an AFDX network, building on the A380’s experience.

The Boeing 787 Dreamliner uses AFDX, which uses fiber optic connections instead of copper ones.

Through agreements with Selex ES and Vector Informatik GmbH, Airbus and its parent company, EADS, have made AFDX licenses available through the EADS Technology Licensing initiative.

Technical specifications of AFDX

Full duplex, redundancy, deterministic, high-speed performance, switched, and profiled network are the six main components of AFDX.

To put the entire system together, the library can be linked to the hardware and software building blocks of the architectural library.

Any topology, even a star, is capable of being used by the AFDX switch.

- All connections are full duplex

- Data rate at 100 Mbits/sec

- Supports multiple Virtual Links- vLAN with variable BAG and LMax values

Aircraft Data Network (ADN) is a concept in the ARINC 664 Specification defined by the Airlines Electronic Engineering Committee (AEEC).

Data networking standards proposed for use in commercial aircraft installations are recommended in this document.

The standards provide a way to apply Commercial off-the-shelf (COTS) networking standards to an aircraft system.

It refers to devices and their use, such as bridges, switches, routers, and hubs, in an aircraft system.

When set up in network topology, this equipment can provide efficient data transfer and overall avionics efficiency.

The specification of ARINC 664 refers extensively to the set of standards developed for data networking by the Internet community and IEEE.

Across several sections, the specification is organized as follows:

- Part 1 – Systems Concepts and Overview

- Part 2 – Ethernet Physical and Data-Link Layer Specifications

- Part 3 – Internet-based Protocols and Services

- Part 4 – Internet-based Address Structure and Assigned Numbers

- Part 5 – Network Domain Characteristics and Functional Elements

- Part 6 – Reserved

- Part 7 – Deterministic Networks

- Part 8 – Upper Layer Protocol Services

The physical layer consists of an Ethernet network of star topologies with End Systems and layer two switches. Using Virtual Links (VL) is the defining characteristic of the network.

Components of AFDX

Avionics Subsystem:

The flight control computer, GPS, tire pressure monitoring system, and other conventional avionics subsystems aboard an aircraft.

To support the Avionics Subsystems, an Avionics Computer System offers a computing environment.

An embedded end system, which links the avionics subsystems to an AFDX interconnect, is a component of each avionics computer system.

AFDX End System:

Provides an “interface” between the AFDX Interconnect and the Avionics Subsystems.

The End System interface for each Avionics Subsystem ensures a safe and dependable data exchange with other Avionics Subsystems.

The different Avionics Subsystems can now communicate with one another via a straightforward message interface thanks to this interface’s export of an application program interface (API).

AFDX Interconnect:

A switched Ethernet interface operating in a full duplex.

It usually comprises an Ethernet frame-forwarding network of switches to the proper destinations.

The conventional ARINC 429 unidirectional, point-to-point technology and the MIL-STD-1553 bus technology are replaced by this switched Ethernet technology.

How AFDX works

Data Flow in AFDX

A VL specifies a logical data path via the shared network. It depicts the flow of data in a single path from a single source to one or more destinations.

The VL is identified by 16 bits in the destination MAC address. This is used by the switches to route the frame appropriately.

Bandwidth allocation

One key component of the AFDX protocol is the bandwidth allocation gap or BAG.

Data can only be sent at this maximum rate, and it will always be sent at that interval.

Attention must be given when determining the BAG rate for each VL to ensure that there is adequate bandwidth for further VLs and that the maximum speed is limited to 100 Mbit/s.

Virtual Links (VLs)

An AFDX network’s virtual links are its main component (VL).

The VLs can be represented as an ARINC 429-style network with one source and one or more destinations in a single abstraction.

Unidirectional logic routes known as virtual linkages connect all of the destination end systems to the source end system.

AFDX routes packets using a virtual link ID, which is carried in the same location in an AFDX frame as the MAC destination address in an Ethernet frame.

In contrast to a standard Ethernet switch, which changes frames based on the Ethernet destination or MAC address.

However, in the instance of AFDX, the data carried is identified by this virtual link ID instead of the actual destination.

The virtual link ID comes after a constant 32-bit field and is an unsigned integer value of 16 bits.

An incoming frame from a single-end system and only one end system can be routed by the switches to a preset group of end systems.

Within each virtual link, there can be one or more receiving end systems connected.

The system integrator determines the overall bandwidth allotted to each virtual link, which is calculated as the sum of all VL bandwidth allocation gap (BAG) rates times MTU.

The overall bandwidth, however, cannot be greater than the network’s maximum accessible bandwidth.

Therefore, the specification of a complementary VL must be necessary for bi-directional communications.

Determinism is the result of each VL’s specification being locked to guarantee that the network has a maximum amount of traffic intended.

Additionally, the switch can reject any incorrect data transfer that might otherwise overwhelm other network branches because it has a VL configuration database loaded.

Sub-virtual connections, or sub-VLs, are another option; these are intended to transport less important data.

A certain virtual connection is assigned sub-virtual links. The virtual cables carry data to send read data in a round-robin fashion.

Furthermore, because of buffering, sub-virtual links cannot guarantee bandwidth or latency; yet, AFDX stipulates that latency must be measured from the traffic regulator function.

Benefits of AFDX in avionics

Enhanced Data Integrity

- The data integrity is significantly enhanced by the AFDX avionics system.

- Error detection and correction features in AFDX provide error-free and dependable data transmission over the network.

- Because the correctness of the data directly affects both the system’s performance and flight safety, it is crucial in the field of avionics.

Real-time Data Transmission

- AFDX excels in transferring data in real time.

- Its switched Ethernet architecture reduces latency and ensures data flow without a single lost second.

- This real-time performance is critical to avionics systems, which depend on timely and accurate information for navigation, control, and monitoring tasks to improve operational efficiency and responsiveness.

Network Efficiency

- Sophisticated traffic management and capacity distribution enhance network efficiency inside AFDX.

- AFDX is used to identify which data are critical so that deterministic data transfer, effective bandwidth control, and priority assignment of important data may be implemented.

- As avionics systems have improved network performance, reduced congestion, and boosted reliability, they can manage complex data transfer without compromising speed or accuracy.

AFDX is a crucial technology for contemporary avionics systems because of these advantages, which guarantee high-performance, dependable, and effective operation in the demanding aircraft application environment.

Applications of AFDX

Commercial Aircraft

Additionally, AFDX leads the way in improving the avionics systems’ overall efficacy and dependability in modern commercial aircraft.

With onboard systems becoming increasingly complex, there is an increasing demand for a fast and dependable data network.

Through the facilitation of efficient data interchange among numerous subsystems, such as flight control, navigation, and in-flight entertainment, AFDX provides smooth data flow and real-time decision-making.

Deterministic in nature, AFDX ensures critical data while enhancing performance and safety.

Military Aircraft

AFDX provides an unrivaled communication backbone for military aircraft, where mission-critical operations demand not only the highest reliability and speed but also the transfer of massive volumes of data for advanced avionics systems, such as electronic warfare, weapons control, and radar.

Thus, AFDX technology supports high-bandwidth data transmission required by advanced avionics systems.

This is how the fault tolerance and redundancy aspects of AFDX allow for functioning in the face of adverse conditions, which are crucial to the mission’s success.

Furthermore, the standardization of AFDX facilitates the integration of different avionics components, enhancing interoperability and lowering the effort required for future upgrades.

Unmanned Aerial Vehicles (UAVs)

AFDX is equally important for unmanned aerial vehicle operations, where real-time data transfer and the highest level of reliability are critical.

To facilitate reliable communication between ground control stations, navigation systems, and onboard sensors, AFDX has been updated for usage in UAVs.

Due to high-speed data transfer, AFDX can thus manage large-scale data transfers, including telemetry, control signals, and high-definition video.

It will guarantee that UAVs do complex tasks with a high level of accuracy and efficiency, such as surveillance, reconnaissance, and precise targeting.

From small drones to large unmanned aircraft, AFDX is the ideal choice for a wide range of UAV applications due to its scalability and versatility.

AFDX technology is revolutionizing avionics by providing a scalable, reliable, and fast communication network that can meet the demands of modern aerospace applications.

AFDX enhances the avionics systems’ interoperability, performance, and safety in unmanned aerial vehicles (UAVs), military, and commercial applications.

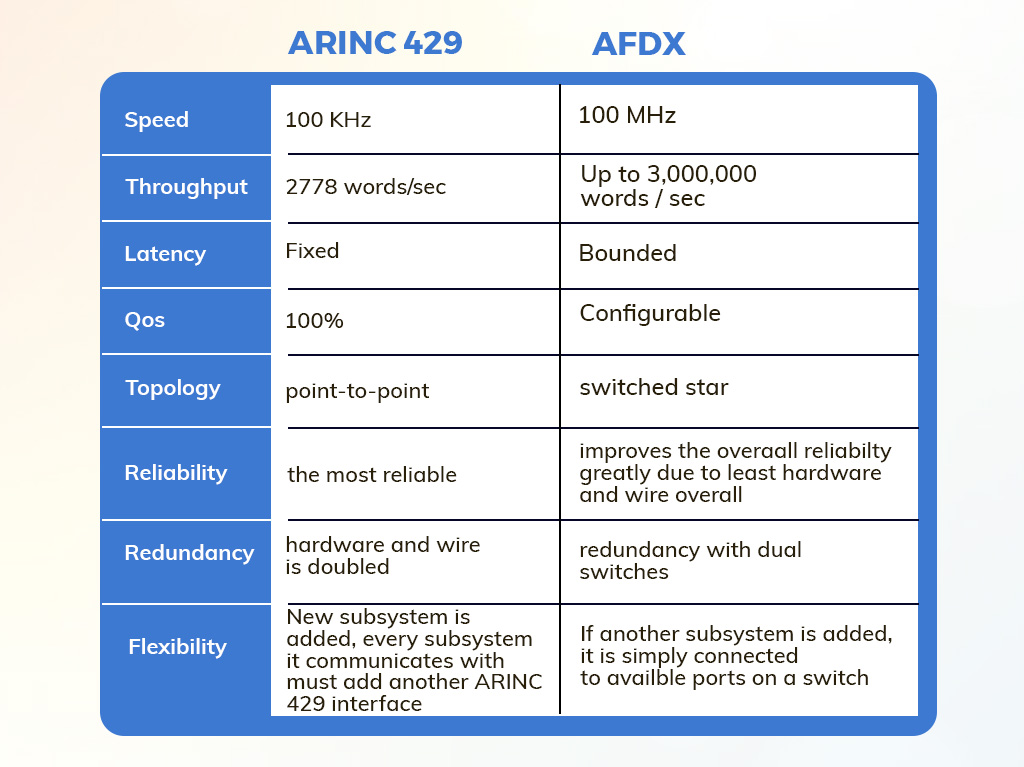

Comparison of AFDX with ARINC 429

AFDX

AFDX or Avionics Full-Duplex Switched Ethernet, has emerged as a crucial element in the automobile, aerospace, and industrial domains of the dynamic communication technology environment.

AFDX is made to meet the rigorous needs of aviation systems and offers deterministic, fault-tolerant communication. It interfaces with industrial standards like ARINC 664 and IEEE 802.3 with ease.

ARINC 429

The primary avionics data bus used on the majority of higher-end commercial and transport aircraft is designated as “Mark 33 Digital Information Transfer System (DITS),” or ARINC 429 in technical terms.

It describes the data protocol and physical and electrical interfaces of a two-wire data bus that supports the local area network of an aircraft’s avionics.

AFDX Vs ARINC 429

Avionics full-duplex switched Ethernet (AFDX) technology enables deterministic Ethernet networking for avionics and aircraft systems.

The 100 Mbit/s AFDX LFT End System card supports rate-constrained traffic shaping to ensure bounded latency and jitter for deterministic Ethernet networking, as described in ARINC standards.

The card can be used for production system integration and provides high-integrity redundancy management as well as an IP/UDP profiled communication layer fully implemented in hardware.

ZYNQ is an ARM SoC-based FPGA from Xilinx. It includes a Dual-core ARM A9 CPU, a high-speed transceiver for PCIe support and 2x Tri-mode Gigabit Ethernet making it a suitable candidate for AFDX implementation.

The host communicates with the AFDX Card via a dedicated driver. The driver uses DMA for fast data transfers between the host and the AFDX Card.

The on-board ARM processor in ZYNQ runs the AFDX protocol stack offloading the host processors executing user applications. For efficient protocol processing, all IP/UDPs are implemented in the programmable logic fabric of ZYNQ. The receive and transmit buffers may be configured to operate as either sampling ports or queuing ports.

A sampling port utilizes a single message buffer while a queuing port contains storage for multiple messages in a FIFO configuration.

Features

- Integrity checking and redundancy management.

- 1 us. Rx frame time-stamp resolution.

- IP/UDP Offloading on hardware.

- Profiled IP/UDP, sampled and queued ports.

- PCI Express and DMA support.

Interfaces

- PCI Express form factor module.

- 2 ports 10/100 Mbit/s Ethernet.

Power Supply

- Single +12V power supply.

- About 7W of power consumption.

Environmental Operating Ranges

- Operating Temp : -40oC to +80 oC

- Humidity Level : 0 to 95%

- Vibration Sine: 3g peak

- Vibration random: 0.1g2 /Hz.

Frequently Asked Questions about AFDX

What makes AFDX unique in avionics?

By extending standard Ethernet, AFDX provides deterministic timing and strong data integrity. Furthermore, a redundant pair of networks is used to reinforce system integrity (a virtual link can be configured to use either one network or the other).

How does AFDX ensure data integrity?

Using twisted pair or fiber optic cables, full-duplex Ethernet transmits and receives data using two distinct pairs or strands. Through the extension of regular Ethernet, AFDX provides deterministic timing and strong data integrity.

What are the challenges in implementing AFDX?

However, it is becoming more challenging to define AFDX topologies that meet certified criteria and are both cost-effective due to the increasing bandwidth demand of IMA systems. The necessary safety and certification processes will add to the delay before these systems are deployed in commercial aircraft.

What is the frame size of AFDX?

In AFDX networks, 64 bytes is the lowest frame size and 1518 bytes is the maximum frame size. The values of these parameters are fmin = 17 bytes, fmax = 1471 bytes, and c = 47 bytes.

What is the origin of Arinc 664 AFDX?

Initially for the A380, Airbus developed and patented the Avionics Full Duplex Switched Ethernet (AFDX®) data network to solve real-time issues for safety-critical avionics applications. AFDX® is an implementation of deterministic Ethernet that conforms to ARINC Specification 664, Part 7.

Conclusion

With AFDX, data communication within aircraft systems is facilitated by a reliable and effective architecture that has completely changed the avionics environment.

Its advanced features, which include virtual linkages and precise bandwidth allocation, provide dependable and flawless data transmission, which is essential for the effective and safe functioning of contemporary aircraft.

AFDX will play a more crucial role as aviation technology develops, handling the avionics systems’ increasing complexity and needs in unmanned aerial, military, and commercial applications.

AFDX represents innovation in aviation technology by bridging the gap between the requirements of next-generation aircraft and the conventional ARINC 429 standards.

This results in a new standard for safety, dependability, and efficiency in the industry.