From JESD204B to JESD204D: As high-speed data applications get better, more people want tools that are faster, more efficient, and more reliable.

Whether in modern medical imaging, 5G wireless networks, or aircraft radar systems, the capacity to convey vast amounts of data rapidly and precisely is essential.

Meeting these requirements is precisely where the JESD204 family of JEDEC standards plays a key role, evolving to support increasingly high-performance systems.

From JESD204B to JESD204D, this blog walks you through each standard’s salient characteristics, uses, and cutting-edge intellectual property solutions from Logic Fruit Technologies that make them possible.

This guide describes the JESD204B, JESD204C, and JESD204D standards and their function in high-speed data transfer, regardless of whether you’re an FPGA developer or system designer.

JESD204 & its evolution

JESD204 (2006)

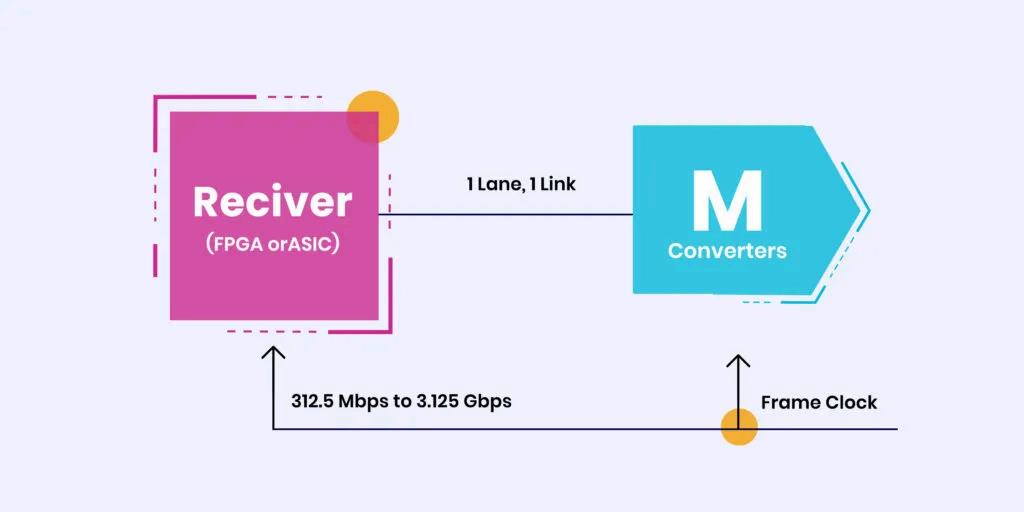

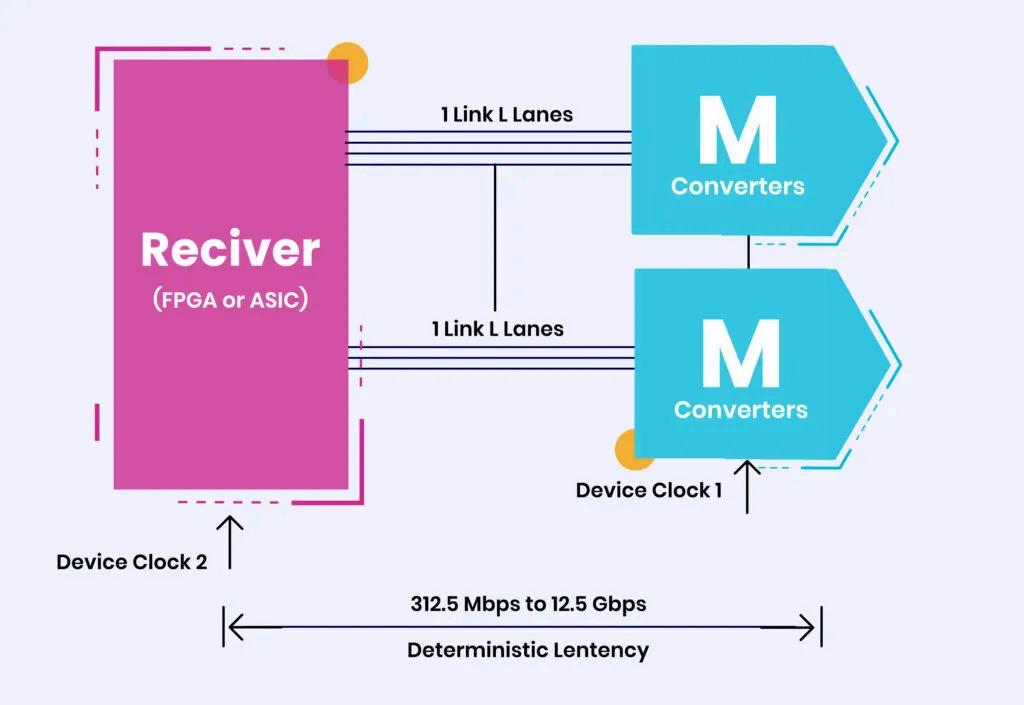

The initial release of JESD204 was in April 2006. A multi-gigabit serial data link between converter(s) and a receiver, typically a device like an FPGA or ASIC, is described in the standard.

A single serial lane connecting a converter or several converters to a receiver was the definition of the serial data link in this edition.

The physical interface, represented by the lane, is made up of a differential pair of interconnects that use current mode logic (CML) to connect the M number of converters to the receiver.

The serialized data link that is created between the converter(s) and the receiver is represented by the link.

The frame clock serves as the clock for the JESD204 link between the converter(s) and the receiver in addition to being routed to both of them.

The source and load impedance are both stated as 100? ±20% and the lane data rate is defined as falling between 312.5 Megabits per second (Mbps) and 3.125 Gigabits per second (Gbps).

It is characterized as having a common-mode voltage level range of 0.72 V to 1.23 V with a nominal peak-to-peak differential voltage level of 800 mV.

To avoid routing an extra clock line and the accompanying complication of aligning an additional clock signal with the transmitted data at high data rates, the link uses 8b/10b encoding, which has an integrated clock.

Comparing this type of serial data transfer to synchronous-sampling parallel LVDS and CMOS interface designs, a trace-to-trace tolerance relaxation is possible.

Furthermore, the encoding is DC balanced, which ensures a substantial transition frequency for applications involving clock and data recovery (CDR) architectures.

Additionally, data and control characters that define link alignment, upkeep, and monitoring can be used thanks to the encoding.

To align the data on the lane between the converter(s) and the receiver over the connection, the standard provides training patterns using these control characters.

The receiver keeps track of the link’s quality and establishes and drops connections according to the JESD204 standard’s specified error thresholds.

When supporters realized that the standard required to enable multiple, aligned serial lanes with numerous converters to handle converters with ever-increasing speeds and resolutions, they changed it accordingly.

JESD204B:

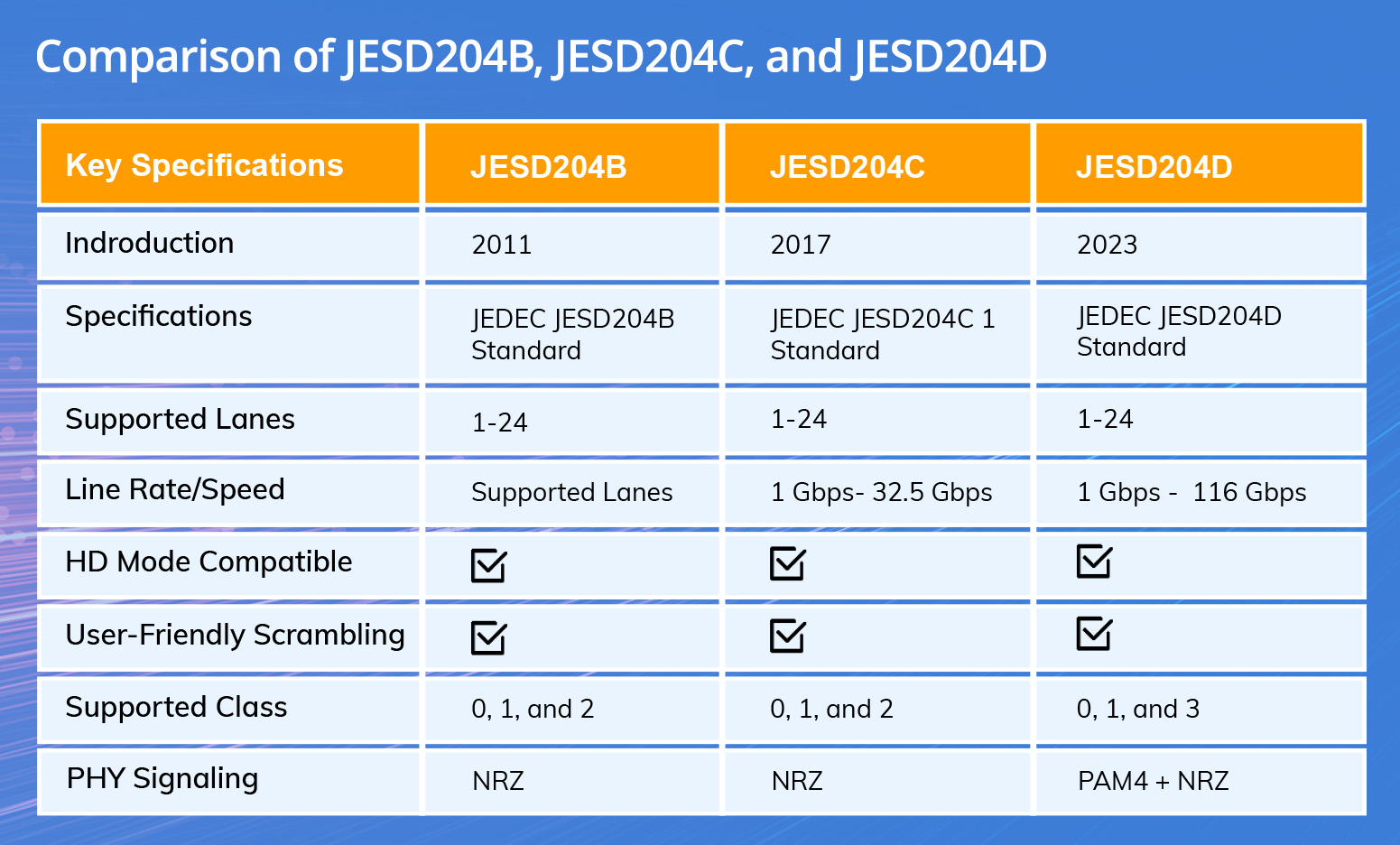

JESD204B, introduced in 2011, added groundbreaking subclasses, lending greater flexibility in multi-device synchronization, most notably introducing deterministic latency. It is also four times faster and enables harmonic clocking.

JESD204C:

In 2017, JESD204C was introduced, which greatly increased serial data rates.

It is more than 2.5 times faster than JESD204B at 32 Gbps.

It contains 64/66B and 64B/80B link layers for clock recovery and receiver training, as well as equalization with lower overhead, in addition to the 8B/10B link layer included in the previous version.

JESD204D:

Maintaining backward compatibility, JESD204D is the latest JESD204 standard, supporting data rates up to 116 Gbps per lane with improved synchronization and greater scalability for ultra-high-speed data converter interfaces.

JESD204B

The standard’s second version, JESD204B, was published in July 2011. The addition of clauses to provide deterministic latency was one of the updated standard’s main elements.

Furthermore, the data rates that were supported were increased to 12.5 Gb/s and divided into various device speed grades.

The device clock should be used as the primary clock source instead of the frame clock, according to this edition of the standard.

The JESD204 standard does not include any mechanisms to guarantee predictable latency across the interface in its first two iterations.

The JESD204B revision addresses this problem by offering a way to guarantee that the latency is predictable and repeatable both across connection resynchronization events and from power-up cycle to power-up cycle.

Applications of JESD204B

Some of the applications of JESD204B are,

1) Wireless Communication Systems

JESD204B is used in wireless communication systems due to its ability to support high-speed data transmission. It supports high bandwidth with fewer pins to simplify the layout.

2) Radar systems

JESD204B is used in radar and sonar systems due to its ability to handle high-speed data processing.

3) Software-defined radios

SDRs are used in JESD204B due to their high-speed data transfer capabilities. A hundred megabytes of Data per second can be easily exchanged between FPGAs and data converters in both the transmitter and receiver modes.

4) Medical Imaging Systems:

JESD204B enables efficient data transfer in medical imaging devices such as MRI machines, CT scanners, and ultrasound systems. High-resolution image data can be transmitted reliably.

Exploring the Power of JESD204B: Unlocking High-Speed Data Transfer

Logic Fruit’s JESD204B Transmitter and Receiver IP

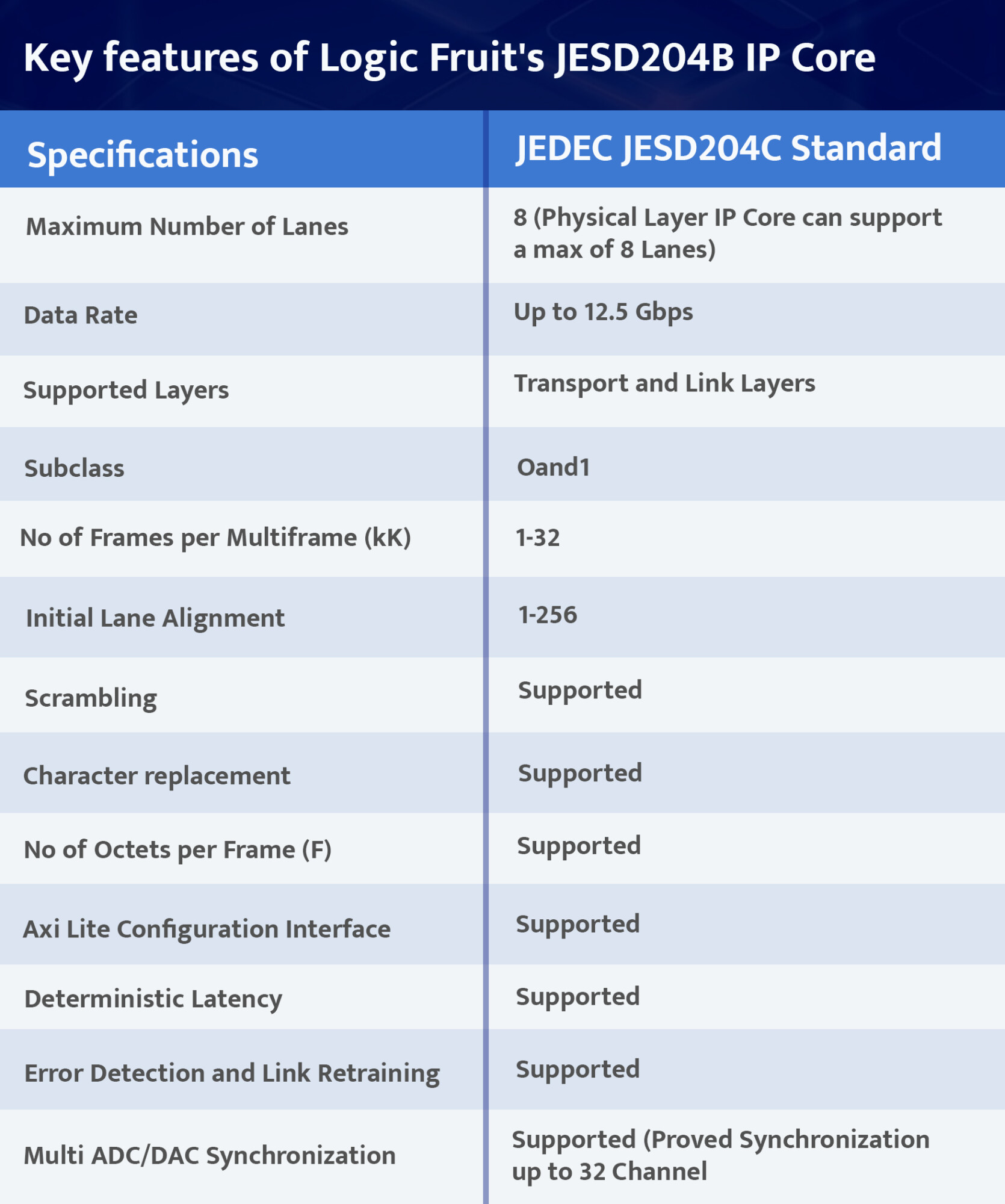

Logic Fruit Technologies’ JESD204B IP core is a high-performance, configurable RTL solution designed for high-speed data transfer in applications such as aerospace, defense, and high-performance computing.

Supporting lane rates up to 12.5 Gbps, it can operate as a transmitter or receiver and uses an 8B10B link layer to provide deterministic latency, SerDes synchronization, clock recovery, and DC balance, ensuring reliable and precise data communication across high-bandwidth systems.

Features and Benefits of Logic Fruit JESD204B IP Core

High Bandwidth Support: Enables RADAR and Medical Imaging systems to handle more channels with fewer pins, simplifying PCB layout.

High Frequency Scalability: Ideal for Wireless Communications, TDMA, and OFDM-based technologies such as LTE and WiMAX, supporting high-speed data transfer.

Reduced PCB Area: Facilitates high-density systems by minimizing board space and package size requirements.

Efficient Power Usage: Maintains comparable power consumption even for large throughput applications.

Serial Interface Support: Provides a robust interface for serializing devices in system designs, reducing space, power, and overall cost.

Deterministic Latency: Ensures predictable data timing across the serial link for real-time applications.

IP Features of JESD204B

Logic Fruit has developed an RTL IP for JESD204B, and here we are showcasing several key features:

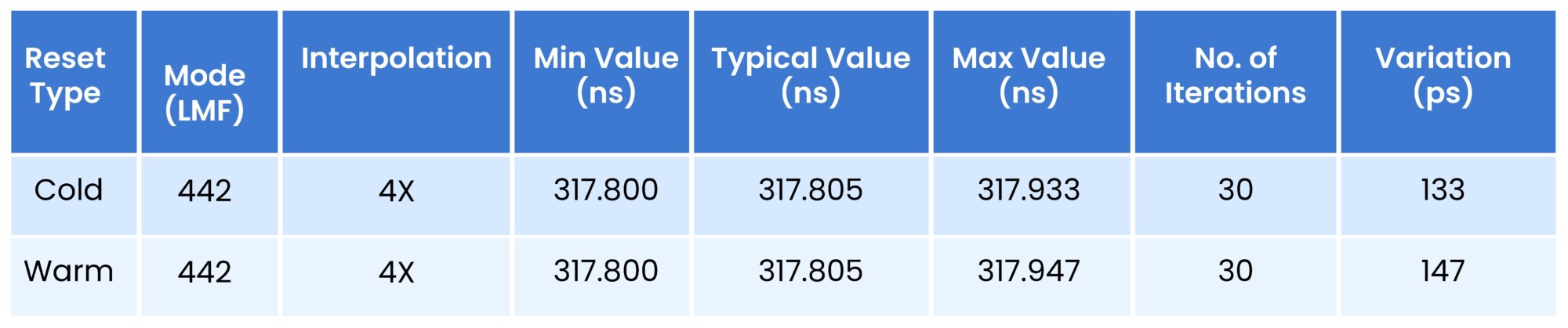

Logic Fruit Technologies’ whitepapers provide detailed performance insights for its JESD204B IP cores, including deterministic latency measurements and flexible lane and frame configurations, demonstrating reliable and predictable high-speed data transfer for both DAC and ADC implementations.

ADC Testing with LFT JESD204B RX IP ported on Efinix Evaluation Board

DAC Testing with LFT JESD204B TX IP ported on Efinix Evaluation Board

Our Demo Series of JESD204B

JESD204B IP Demo with Lattice FPGA and TI Data Converters

JESD204B Deterministic Latency Demo with Efinix FPGA & TI Converters

To know more about the key specifications and benefits of Logic Fruit’s JESD204B Transmitter and Receiver IP, download the datasheet now!

JESD204C

To meet the increasing performance requirements for both this generation of multigigabit data processing systems and those of the future, the most recent modification of the standard, JESD204C, was released in late 2017.

Four overarching objectives were set by the JESD204C subcommittee for this new standard revision: lane rates should be increased to accommodate the demands of even greater bandwidth applications; payload delivery efficiency should be enhanced; and link robustness should be addressed.

Additionally, they intended to address some of the faults in the JESD204B version of the standard and provide a specification that was clearer than that one.

Additionally, it was intended that JESD204B have a backward-compatible alternative. JEDEC has the whole JESD204C specification available.

This two-part primer introduces the JESD204C standard by outlining its key features and differentiating it from JESD204B.

It also aims to meet the previously mentioned objectives of improving interface usability and providing the bandwidth capability required by a range of industries.

Applications of JESD204C

Almost any system that uses data converters operating at high gigabit and megabit data speeds can benefit from the JESD204C interface. A selection of the applications consists of,

- Test instruments

- 5G cellular equipment

- Other cellular base-station gear

- Medical Apparatus

- Military/electronic warfare (EW)

- Satellite

- Almost any direct-conversion software-defined radio (SDR)

JESD204C – Everything You Need to Know

Logic Fruit’s JESD204C Transmitter and Receiver IP

Logic Fruit Technologies’ JESD204C IP core is a high-speed, configurable transmitter and receiver supporting lane rates up to 32 Gbps.

It uses 64B66B or 8B10B link layers for efficient and robust data transfer and is backward compatible with JESD204B, enabling flexible, high-bandwidth system designs.

Features and Benefits of Logic Fruit JESD204C IP Core

Error Correction (FEC): Enables cutting-edge instrumentation and other applications to operate without errors.

Improved DC Balance: Offers better clock recovery and data alignment compared to JESD204B.

Low Bit Overhead: Achieves only 3.125% overhead, significantly lower than JESD204B (~25%), improving efficiency.

Serial Interface Support: Provides a robust interface for serializing devices, reducing space, power, and cost.

High-Speed Data Support: Meets interface requirements for high-megabit and gigabit data rates in applications like 5G, test equipment, medical devices, and defense systems.

Deterministic Latency: Ensures predictable and reliable data timing across the serial link.

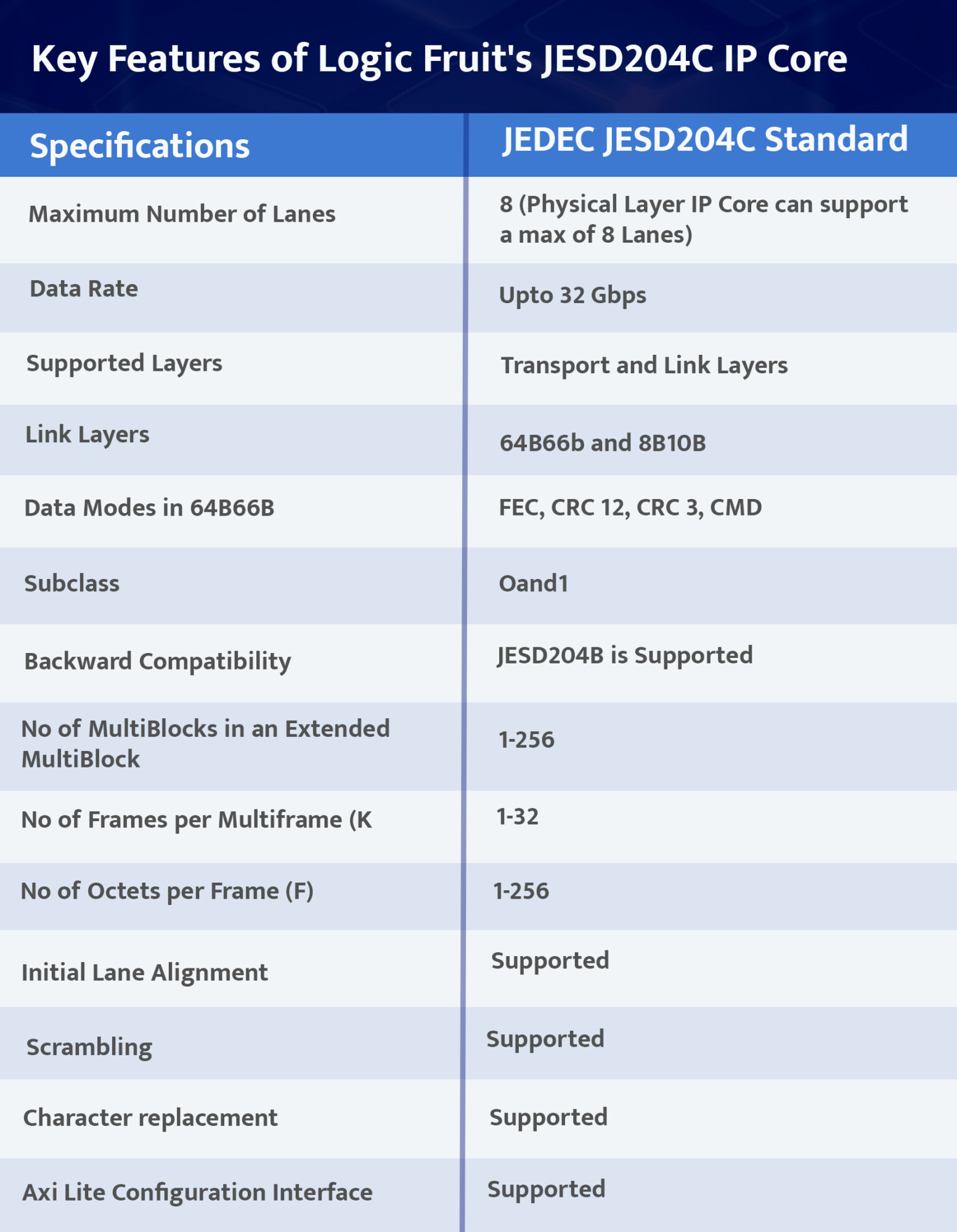

Logic Fruit’s JESD204C IP Core Features:

Logic Fruit has developed an IP Core designed specifically for JESD204C, and here are some of the IP Features of Logic Fruit’s JESD204C IP Core

JESD204B vs JESD204C: Key Differences You Must Know

JESD204C Setup and Testing Demonstration

This video demonstrates the Achronix JESD204C setup, including linkup tests, adapter board usage, and RX/TX block diagrams. It also analyzes waveforms and frequencies, providing a clear overview of JESD204C link performance and validation.

To know more about the key specifications and benefits of Logic Fruit’s JESD204C Transmitter and Receiver IP, download the datasheet now!

JESD204D

The JESDC standard’s newest JESD version, JESD204D, addresses this by increasing lane rates, using advanced error correction techniques, and retaining backward compatibility with older standards.

With major improvements and backward compatibility, the most recent version, JESD204D, builds on the developments of JESD204C and JESD204B.

PAM4 signaling is introduced for data speeds as high as 116 Gbps, and JESD204D provides NRZ (PAM2) signaling at up to 58 Gbps.

PAM4 is a logical step toward greater line rates; however, to handle its higher Bit Error Rate (BER), RS-FEC (Reed Solomon Forward Error Correction) encoding is needed.

While NRZ links employ FEC techniques for error detection, displacing the CRC approach, JESD204D guarantees robust error detection and correction for PAM4 links with RS-FEC encoding as a crucial addition.

Because of this development, JESD204D is perfect for high-bandwidth defense, aerospace, and telecommunications applications.

Applications of JESD204D

5G/5G NR/6G: Enables fast, low-latency data transfer in wireless networks.

Aerospace/Defense: Supports synchronized data for radar and avionics.

Automotive/ADAS: Powers real-time processing for autonomous vehicles.

Medical Imaging: Provides high-resolution, real-time diagnostics.

Test/Measurement: Delivers synchronized, high-speed data acquisition.

JESD204D: Revolutionizing High-Speed Communication

Logic Fruit Technologies JESD204D Transmitter and Receiver IP

Logic Fruit Technologies’ JESD204D IP core is designed to support ultra-high-speed data transfer with increased lane rates for higher bandwidth applications.

Backward-compatible with JESD204C and JESD204B, it works seamlessly with leading ADCs and DACs from multiple vendors.

Building on its experience with JESD204B and JESD204C, Logic Fruit continues to pioneer JESD204D IPs for FPGAs, delivering innovative solutions for advanced, high-performance systems.

Logic Fruit JESD204D IP Features

JEDEC Standard Compliance: Designed according to the JESD204D standard for ultra-high-speed data transfer.

Lane Support: Supports up to 24 lanes per IP core for high-bandwidth applications.

Error Correction (RS-FEC): Implements Reed-Solomon Forward Error Correction for improved link reliability.

Backward Compatibility: Offers options to support JESD204C (64B/66B encoding) and JESD204B (8B/10B encoding).

Transport Layer: Enables multi-ADC/DAC synchronization and management of multiple lanes.

High-Speed Data Interfaces: Supports up to 116 Gbps with PAM4 encoding and up to 58 Gbps with NRZ encoding.

Subclass Support: Compatible with JESD204D subclasses 0, 1, and 3.

New JESD204D Features: Implements all additional enhancements introduced in the JESD204D specification.

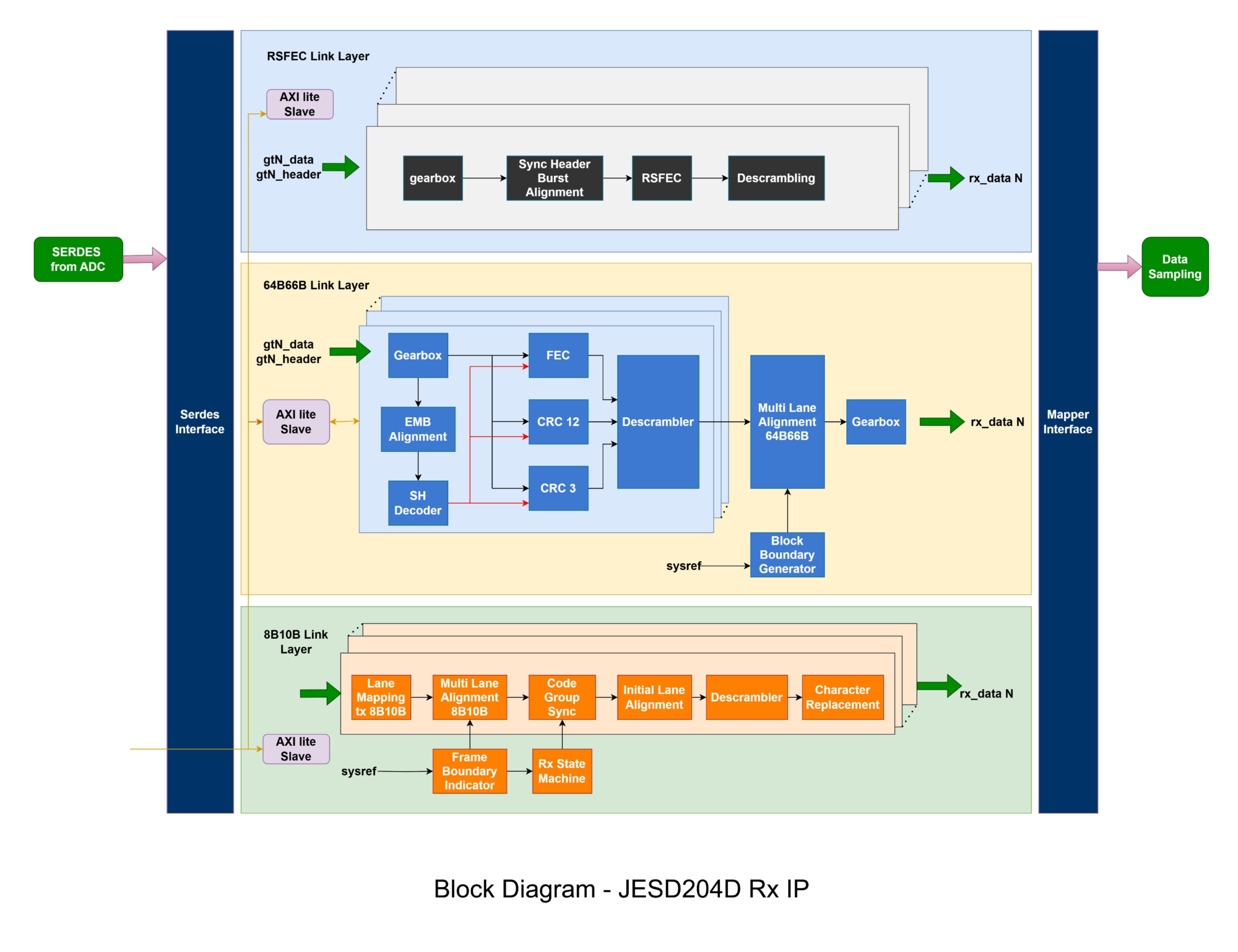

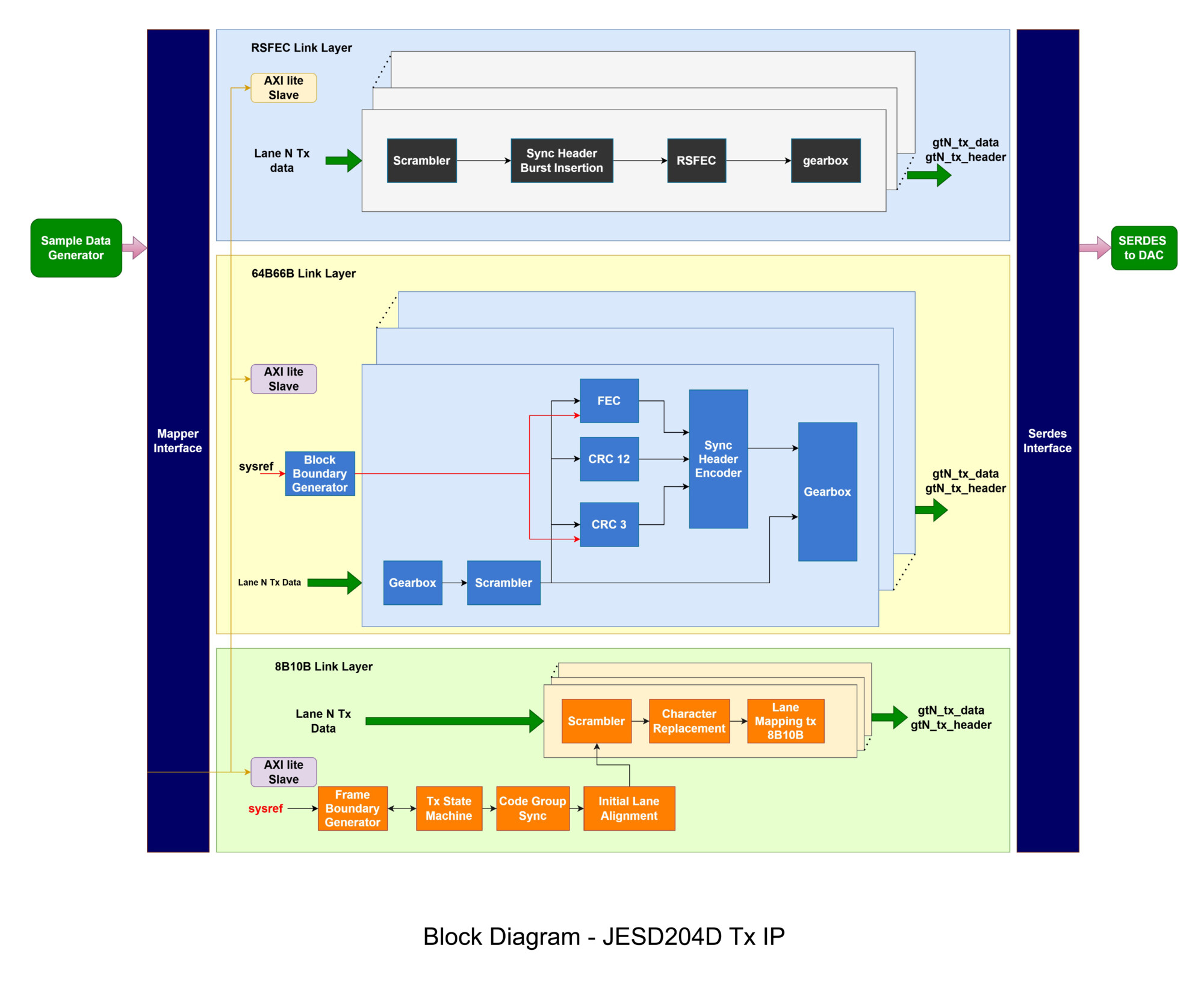

Logic Fruit’s JESD204D Rx & Tx IP Block diagram

To know more about the specifications of Logic Fruit’s JESD204D Transmitter and Receiver IP, download the datasheet now!

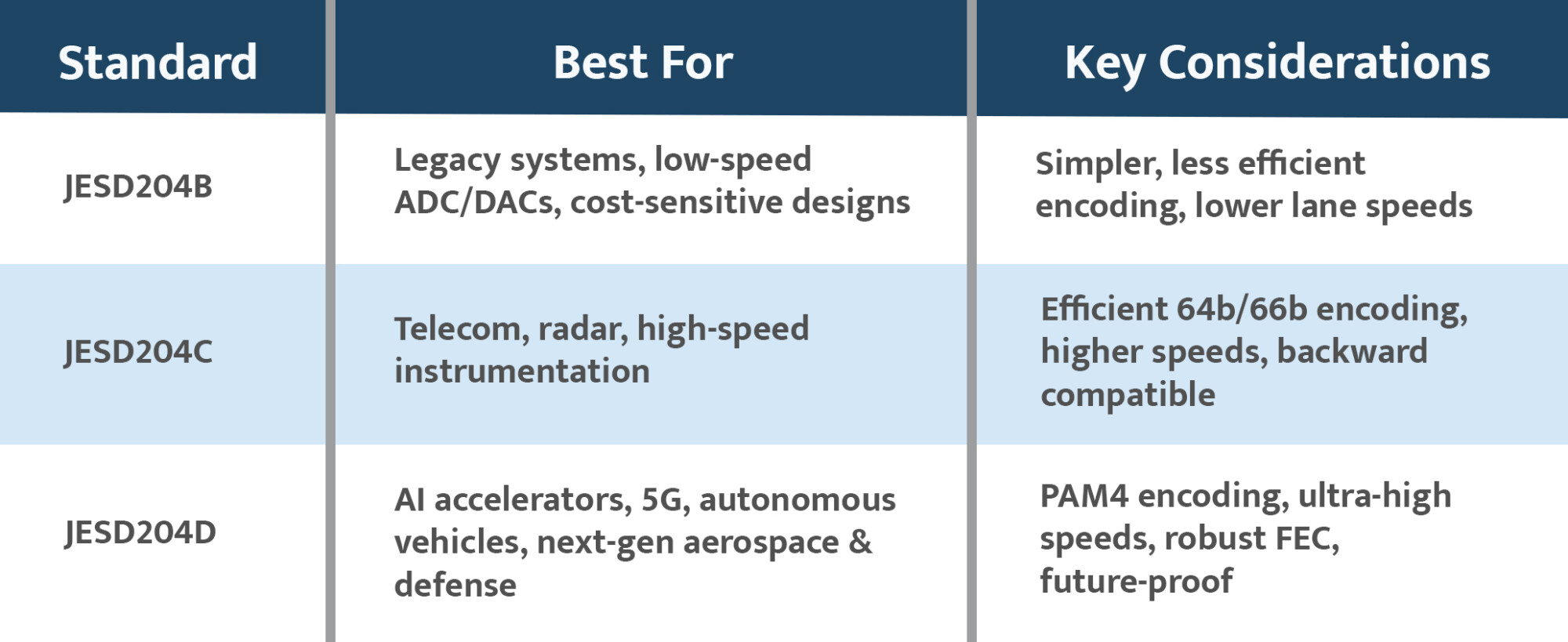

Choosing the Right JESD204 Standard based on the Application Suitability

Conclusion

The transition from JESD204B to JESD204D demonstrates how modern electronics are increasingly demanding predictable latency, larger bandwidth, and effective multi-lane data transfer.

Every version of the standard adds additional features, such as scalable high-speed interfaces and enhanced connection efficiency and error correction.

Complex applications in wireless communications, medical imaging, aerospace, and defense can now be addressed thanks to these developments.

These characteristics are utilized by Logic Fruit Technologies’ JESD204 IP cores, which offer adaptable, reliable, and efficient solutions for both DAC and ADC systems.

Designers can simplify system integration, lower PCB complexity, and provide dependable, predictable data flow by using these IP cores.

In the end, engineers can create next-generation systems that satisfy the exacting requirements of today’s high-performance applications by comprehending and putting into practice JESD204 standards.