Video acquisition systems are at the front of technological progress in a world where visual data drives decisions, insights, and inventions.

These advanced systems take in and filter high-quality video feeds from multiple sources, turning unprocessed material into information that can be used in a variety of businesses.

With the increasing demand for real-time, high-definition video, these systems are developing to meet the demands of our ever-changing environment and make every frame matter in our pursuit of accuracy and clarity.

This blog analyzes the definition of video collection systems, the various varieties that are out there, and the wide range of uses for them, including aiding autonomous vehicles, medical operations, and broadcast experiences in addition to improving security.

What is a Video Acquisition system?

A video acquisition system is an all-in-one setup intended to capture and process video data.

The Video Acquisition system records, analyzes, and stores video data by converting real-time visual information into a digital format so that such information can be used for analysis, monitoring, or broadcasting.

Such systems have many applications nowadays, from surveillance to broadcasting, automotive technology, and medical imaging fields.

Video acquisition needs to deliver state-of-the-art image and audio quality to provide a stand-out consumer experience.

Cameras and microphones are used for content capture and processing, while different connectivity solutions carry the content through the network to the video production equipment

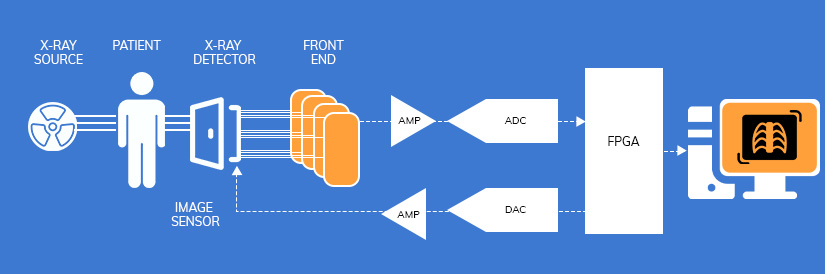

Source – https://www.researchgate.net/figure/Block-diagram-of-a-video-acquisition-system_fig3_281551612

According to Grand View Research, With a projected value of USD 11.70 billion in 2022, the global market for video management systems is expected to increase at a compound annual growth rate (CAGR) of 20.3% between 2023 and 2030.

One major driver propelling the market’s growth is the quick implementation of video management systems (VMS) for surveillance and traffic control.

These technologies, which monitor several closed-circuit television (CCTV) video feeds from diverse locations in a single network operations center, are essential for enhancing traffic safety and averting traffic accidents.

Adopting VMS to lower traffic injuries and accidents is becoming more and more popular in various nations.

Components of a Video Acquisition System

Cameras: The main input devices in a video acquisition system are cameras. They take in visual information from their surroundings and translate it into electrical signals.

There are several kinds of cameras in use, and each has unique characteristics designed for a particular purpose:

- Analog Cameras: Traditional cameras that use analog signals. In order to convert the analog signal into a digital format, they frequently need extra equipment.

- Digital Cameras: These cameras directly record video in digital format, which streamlines the steps of processing and storing.

- IP Cameras: Video is transmitted via network connections using Internet Protocol (IP) cameras, which provide scalability and flexibility for a range of applications.

- Capture Hardware: A video acquisition system relies heavily on capture hardware, such as frame grabbers. By interacting with the cameras, it records and transforms video data into a digital format that a computer can understand. Several interfaces, including USB, HDMI, and SDI, can be used to link this devices to cameras.

Processing Units: When the video data is captured, it is handled by processing units, which might comprise both CPUs and GPUs (graphics processing units).

They carry out activities like encoding, decoding, and real-time processing.

The needs of the application, such as real-time video analytics or high-definition video rendering determine whether CPU or GPU processing is preferable.

Storage Solutions: Managing the recorded video data requires storage options.

Video data can be stored remotely using cloud storage or locally on hard drives, depending on the application.

With options for high-capacity and high-speed data retrieval, effective storage solutions guarantee that video data is readily available and manageable.

Types of Video Acquisition Systems

Systems for capturing, processing, and storing video data from several sources are known as video acquisition systems.

The complexity and configuration of these systems might vary greatly depending on the application.

Below is a summary of the primary categories of video acquisition systems along with their distinct attributes:

- Single Camera System

- Multi- Camera System

Single Camera System

As the name implies, a single camera system in embedded vision systems uses a single camera module to capture images and movies.

The properties of the camera, such as resolution, frame rate, shutter type, chroma (color vs. monochrome), dynamic range, focus type (autofocus vs. fixed focus), interface, etc., are the only factors considered by engineers when selecting a single camera system.

However, a single camera system might not be able to record the whole scene or cover a large region due to the field of view’s restrictions.

Applications that need to monitor huge areas or have a wider field of view may find this to be a drawback.

Even with a wide-angle lens, it is generally not advised to use a single camera when the field of view is as high as 180 degrees because this could cause lens distortions like waveform distortion.

The caliber of the lens you use will also affect this.

The Single camera can be various applications such as,

- Smart traffic systems

- Biometric and security systems

- Medical microscopes

- Document readers

- Industrial handheld scanners

- Eye diagnostic devices

- Digital signage and displays

- Patient monitoring devices

- Surveillance systems

Multi-Camera System

A multi-camera system is a configuration that makes use of two or more cameras to take pictures from different angles.

These cameras can work simultaneously (synchronously) or independently (asynchronously).

Compared to single-camera systems, multi-camera systems offer more visual information, especially for applications involving tracking and identification in three-dimensional space.

Using various cameras to take different kinds of pictures is another scenario.

Take a drone, for example, that is used to assess the Normalized Difference Vegetation Index (NDVI) in precision agriculture. Infrared (IR) images must be captured by one camera, while visible images must be captured by another.

Some of the applications of Multi Camera system are,

- Robotics

- Drones

- Autonomous Shopping

- Airport Baggage systems

- Agricultural and industrial vehicles

How the Video Acquisition System Works

The system is targeted to enhance the quality of the videos from the thermal imager system and equip the images with the capability of video acquisition, video streaming, and video analytics.

Video Capturing Unit and Video Processing Unit will be implemented in the PL portion of the FPGA.

These units will be responsible for receiving PAL video data @ 25 fps and applying some video processing like 2D-FFT/IFFT and Bilateral/Gaussian filtering.

The raw data rate of the frames generated for PAL video @ 25 fps is 20 M-Byte/sec, Ethernet/USB cannot support such high speed.

Hence, it is necessary to compress the video data before streaming it over Ethernet. We’ll use JPEG compression.

The JPEG compressed video can be saved on board in a SD Card present on the board. The saved video will be in the form of a sequence of JPEG images.

The video can later be retrieved from a host PC using a USB interface.

The JPEG-compressed video can be streamed over the Ethernet interface to a PC. A socket connection will be created between the host PC and the ZYNQ board for streaming.

In both the cases of streaming and archival the frame rate may be limited due to (1) limited speed of JPEG compression running on an ARM processor on a ZYNQ board, (2) limited speed of streaming over Ethernet, (3) limited speed of writing into NAND Flash/ SD Card.

Finally, there will be a small application/GUI running on a PC that will have a media player to display the video, and also to control some of the functionalities of video streaming/archival.

The system can be broadly seen as the following simplified block diagram:

Applications of Video Acquisition Systems

Industrial Applications

Video acquisition systems are used in industrial settings for process monitoring and quality control.

Cameras record footage of items and production lines, enabling in-the-moment flaw detection and inspection.

In order to guarantee that the final goods fulfill quality standards, automated systems examine the video feeds. This lowers the possibility of errors and increases production efficiency overall.

Surveillance and Security

Intelligent video surveillance encompasses a broad spectrum of use cases and applications for technologies related to movement analysis, anomaly detection, object tracking and detection, monitoring systems, identification, prevention, and warning.

Large-scale AI vision systems with several cameras integrated at different places are made possible by cooperative video surveillance.

Broadcasting

Video acquisition systems are used in broadcasting to record and broadcast live events, including concerts, sports, and newscasts.

High-definition cameras and capture hardware guarantee that the footage satisfies the requirements for broadcasting and live streaming.

Using multiple cameras improves the viewing experience by offering a variety of viewpoints and angles.

Automotive

Advanced Driver Assistance technologies (ADAS) in automobiles use video acquisition technologies to increase driving enjoyment and safety.

Vehicle-integrated cameras record live footage of the environment around the car, which helps with functions like automated emergency braking, adaptive cruise control, and lane departure warnings.

For these systems to give drivers precise and fast feedback, high-resolution video is necessary.

Medical imaging

Video acquisition systems are employed in the medical industry for minimally invasive operations and endoscopy, among other diagnostic imaging techniques.

Accurate diagnosis and treatment planning are aided by the precise imaging of inside organs and tissues made possible by high-definition video capture.

Access to high-quality visual data for analysis and evaluation is ensured for medical personnel by the capacity to record and capture processes.

Conclusion

Video acquisition systems have completely changed how we record, process, and use visual data.

This has had an impact on a wide range of industries, including media, security, and the automotive and medical sectors.

Their capacity to provide real-time, high-quality video data has opened up new opportunities and improved operational effectiveness in a variety of applications.

These systems are expected to become even more crucial as technology develops, providing unmatched insights and spurring creativity.

By fully utilizing video acquisition technology, we can improve our existing capabilities and lay the groundwork for future innovations that will continue to change the world.

Frequently asked questions

What is the acquisition system?

Acquisition systems are transaction-based information systems that deal with the day-to-day running of the library, such as ordering resources, reeiving them, and handling financial data. They are similar to circulation systems.

What is video processing system?

The term “video processing” describes the computationally demanding operations, such as image processing, compression, color conversion, and encryption, that are involved in handling and modifying video data.

What is a video capture system?

A hardware device that you attach to your computer and which transforms the video signal from your camera’s output into a digital format that your computer can understand is called a capture device, sometimes known as a capture card.

What is video recording system?

Analog security cameras are usually utilized with a DVR. The analog feeds from the cameras are converted into digital format for archiving.

DVRs often feature multiple recording modes, including motion detection, continuous, and scheduled recording, in addition to built-in hard drives for storage.

What is video monitoring system?

A network of cameras, monitors/display units, and recording devices that gather and keep track of visual data in a predetermined region is called a video monitoring system.

It gives the ability to monitor and safeguard individuals, things, or assets in real time or through recorded surveillance of activities.

What is a video management system?

A security camera system’s video management system, sometimes referred to as video management software plus a video management server, generally gathers video from cameras and other sources, and documents or keeps the video on a storage medium.

What are the features of video processing?

Signal processing using statistical analysis and visual filters is what video processing entails in order to extract information or manipulate videos.

Among the fundamental methods of video processing are image resizing, brightness and contrast adjustments, fade in and fade out, and trimming.