An effective interface for tying peripheral devices to computer systems is crucial in the world of modern computing, where data-intensive applications and high-speed communication are crucial.

At this point, PCI Express, often known as PCIe, becomes an essential component. The high-speed serial computer expansion bus standard known as PCI Express has transformed the way peripherals connect to computers.

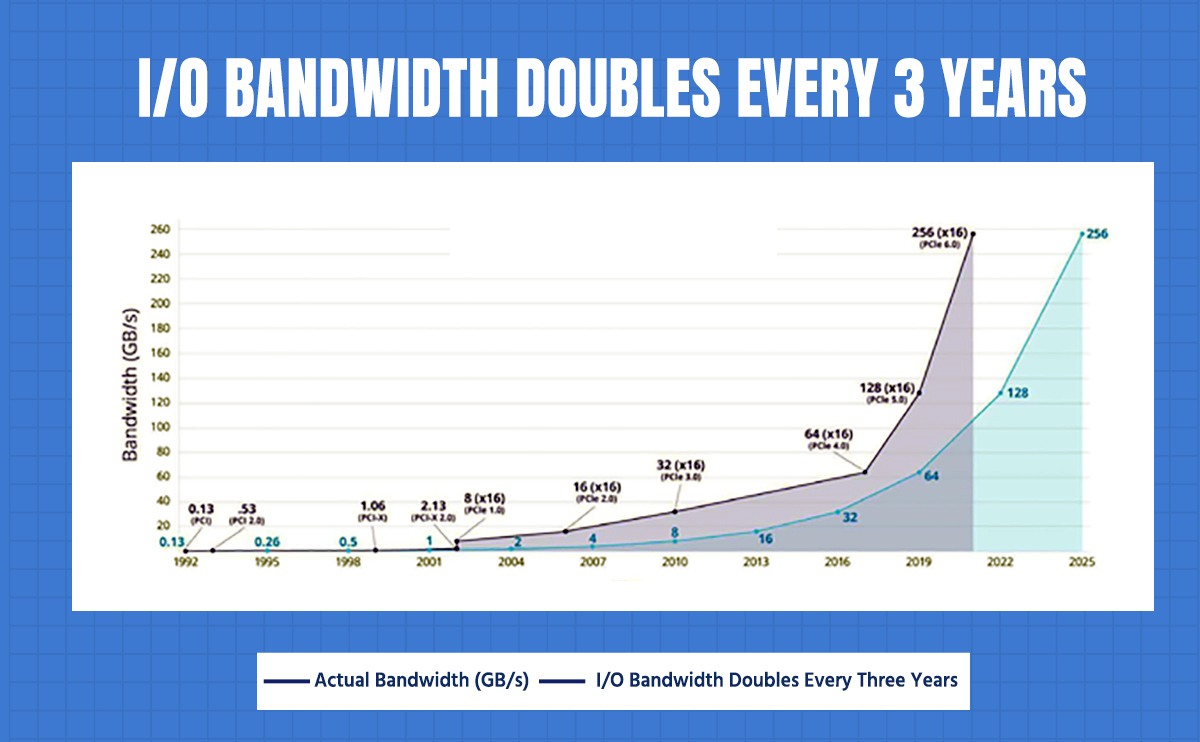

PCIe has seen substantial improvements in terms of speed, bandwidth, and performance since its launch. This progress has advanced to new heights with the most recent version, PCIe 6.0.

Unlock 64 GT/s with our PCIe Gen6 Controller IP. FPGA/ASIC ready, PCI-SIG compliant.

In this blog, we’ll examine PCIe 6.0 in-depth, delving into its technical specifics, contrasting it with earlier generations, looking at industry adoption, and talking about upcoming advances.

You will have a solid understanding of PCIe 6.0 and how it affects high-speed data transport by the time it is all said and done.

So let’s start this adventure to explore the innovations and complexities of PCIe 6.0 and learn why it is regarded as a game-changer for PCI Express!

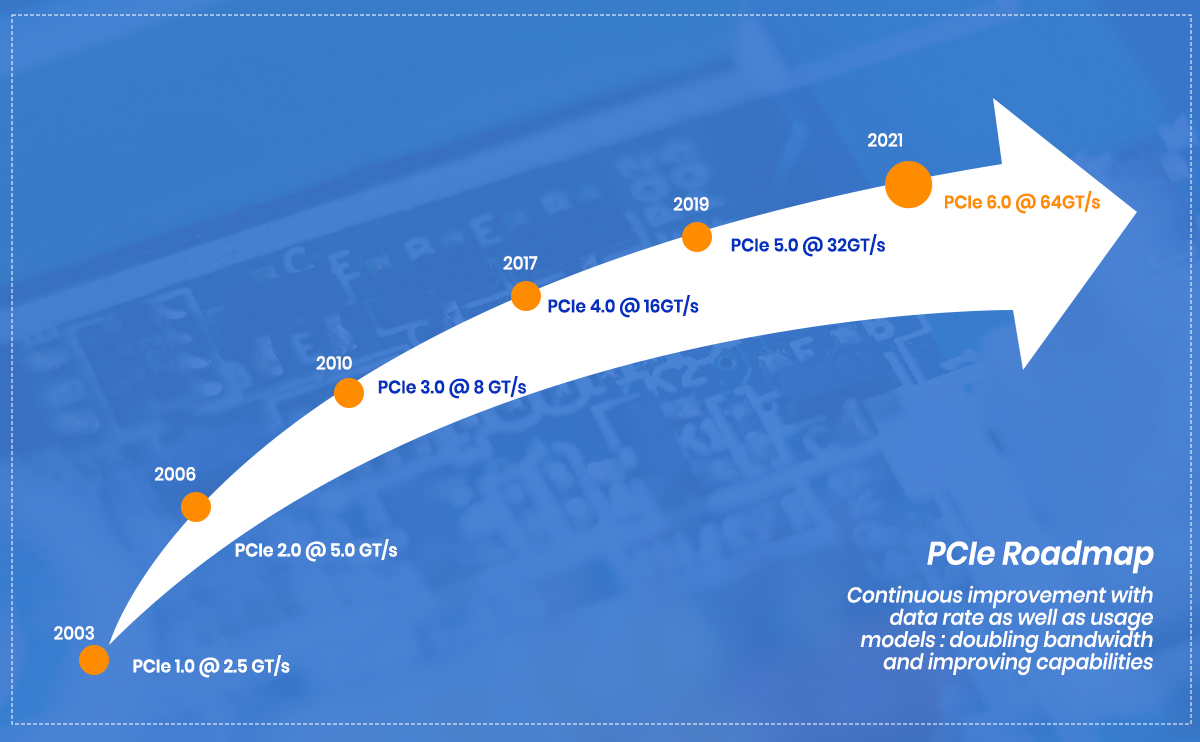

Generations of PCIe

The high-speed interface standard known as Peripheral Component Interconnect Express (PCIe) links CPUs, GPUs, storage devices, and other peripherals to the motherboard.

For data-intensive applications, each new generation offers increased efficiency, reduced latency, and quicker bandwidth.

PCIe 1.0

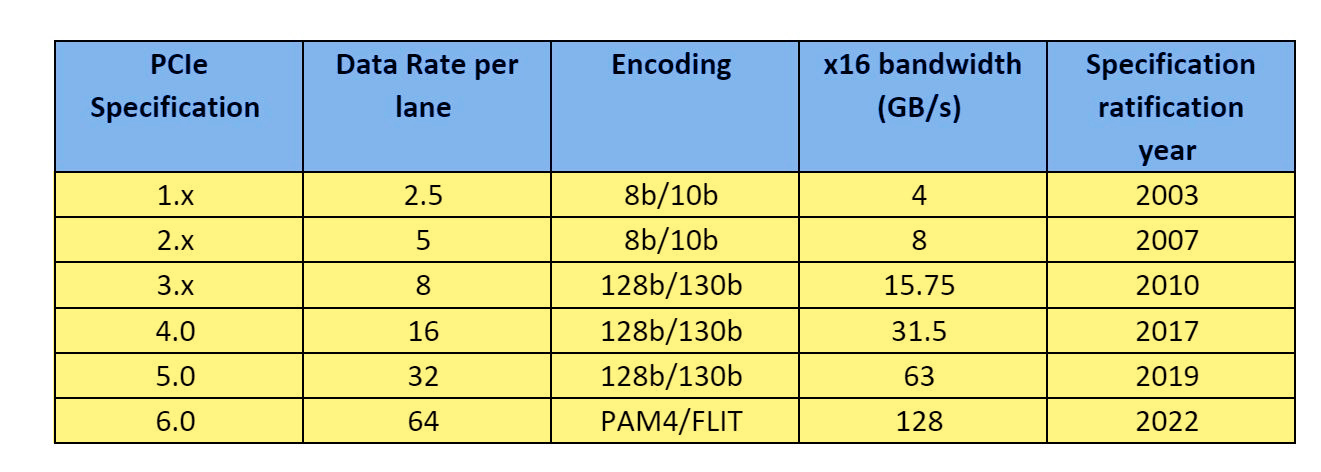

With a serial data rate of 2.5 GT/s and lane widths of x1, x2, x4, x8, and x16, PCIe technology made its debut in 2003. These specifications have been maintained throughout the six iterations.

Despite a 25% encoding overhead, PCIe 1.0’s overall bandwidth of about 4 Gb/s was achieved with the use of 8b/10b encoding for DC balance and packet signaling.

PCIe 2.0

With the introduction of PCIe 2.0 in 2007, the per-lane throughput was quadrupled from 250 MB/s to 500 MB/s, while maintaining complete backward compatibility with PCIe 1.x and 8b/10b encoding.

By supplying the same 4 GB/s bandwidth as Gen 1 with only four lanes instead of eight, it reduced implementation costs for high-bandwidth applications.

It also offered feature and protocol updates, greater slot power restrictions, and more effective link configurations.

PCIe 3.0

PCIe 3.0 was released in 2007, it maintained backward compatibility while increasing the signaling rate to 8 GT/s.

It reduced overhead to roughly 1.5% and essentially doubled the bandwidth of PCIe 2.0 by using a more efficient 128/130b encoding and streamlined protocol rather than leaping to 10 GT/s, which would have required new PCB materials, connectors, and shorter channels.

PCIe 4.0

In order to guarantee cost-effective, power-friendly advancements in materials and packaging, PCIe 4.0, which was announced on June 8, 2017, took longer to arrive but quadrupled the data bandwidth to 16 GT/s.

With the help of enhanced PCB materials like Megatron-2, the channel loss budget rose from 22 dB to 28 dB.

Platforms increased the number of CPU-socket lanes from roughly 40 to up to 128 during the wait, increasing the overall I/O bandwidth and compensating for the lag in per-lane performance increases.

PCIe 5.0

The 2019 release of PCIe 5.0 doubles the speed of PCIe 4.0 to 32 GT/s and provides up to 128 Gb/s of bandwidth in a 16-lane configuration while maintaining complete backward compatibility.

It satisfies the requirements of AI/ML, cloud computing, and data centers.

It supports 400 Gb Ethernet by offering faster I/O and low-latency bandwidth needed for 5G networks and next-generation applications. This is more than most consumer PCs require.

PCIe 6.0

The sixth version PCIe 6.0 doubles the speed of PCIe 5.0 to 64 GT/s while keeping backward compatibility.

Although it has a greater bit error rate than previous generations, it uses PAM4 signaling to overcome channel loss at faster data rates, encoding two bits per symbol for expanded reach.

PCIe-All Generations One-Stop Point Log [Ultimate Guide]

Understanding of PCIe 6.0

PCIe 6.0, also known as PCI Express 6.0, is the latest iteration of the PCI Express (Peripheral Component Interconnect Express) standard, PCIe 6.0, promises ground-breaking speeds and expanded bandwidth.

It is made to meet the rising demands of cutting-edge technology including data centers, high-performance computing, and artificial intelligence.

Purpose: PCIe 6.0 is designed to provide significantly higher bandwidth and faster data transfer rates between components in a computer system.

Release date: PCIe 6.0 was officially released by the PCI-SIG (Peripheral Component Interconnect Special Interest Group) in 2021.

What is PCIe 6.0?

Since PCIe 3, the data rate has doubled with each succeeding iteration of the standard. The data throughput is increased by PCIe 6.0 to 64 Giga transfers per second (GT/s), which is twice as fast as PCIe 5.0.

The link’s bandwidth can reach 128 gigabytes per second (GB/s) for an x16 link, typical of graphics and network devices.

The PCIe 6.0 link is a full duplex, just like earlier versions, and can transmit 128 GB/s of bandwidth simultaneously in each direction for a total bandwidth capacity of 256 GB/s.

Because of its economies of scale, PCIe has spread well beyond servers and PCs. It is appealing for data-centric applications in IoT, automotive, medical, and other fields.

The first PCIe 6.0 deployments will focus on applications that need the most bandwidth feasible and are found in the middle of the data center, including AI/ML, HPC, networking, and cloud graphics.

The following graph shows how the PCIe specification has evolved.

![PCIe 6.0 – All You Need To Know About PCIe 6.0 [2025]](https://www.logic-fruit.com/wp-content/uploads/2023/08/pcle-6.0.png)

Want a visual breakdown? Check out our infographic on PCIe 6.0: Speeding Into the Future.

Key improvements and enhancements over previous versions

- Higher data rate: PCIe 6.0 offers a doubling of the data rate compared to its predecessor, PCIe 5.0. It achieves a raw data rate of 64 GT/s (Giga transfers per second) per lane, resulting in a staggering 256 GB/s (gigabytes per second) in an x16 configuration.

- Increased lane count: PCIe 6.0 supports up to 128 lanes, providing greater scalability and flexibility in terms of device connectivity.

- Forward Error Correction (FEC): PCIe 6.0 introduces new FEC mechanisms to enhance error detection and correction, improving data integrity and reliability.

- Backward compatibility: Despite advancements, PCIe 6.0 remains backward compatible with previous generations, allowing seamless integration with existing PCIe devices.

Although design and efficiency have advanced, attention from both the public and the industry remains fixed on PCIe Gen 6 speed.

Continuing the tradition of doubling bandwidth, PCIe 6.0 delivers record-breaking data rates, unlocking fresh opportunities for the PCIe interface and elevating performance across current applications.

- CXL – Leverages PCIe 5.0’s alternative-protocol support to enable shared memory pools for connected devices, and with PCIe 6.0 gains higher bandwidth for faster, more efficient memory access.

- 800G Ethernet – Requires 100 GB/s across eight lanes; PCIe 6.0’s 128 GB/s x16 link meets the demand for high-density switches and other bandwidth-heavy data-center workloads.

- IoT & 5G – From autonomous vehicles to smart factories, these data-intensive applications benefit from PCIe 6.0’s 64 GT/s speed and low latency to keep pace with massive 5G-driven traffic.

- Military & Aerospace – Advanced satellites, high-resolution sensors, and on-board processing depend on PCIe 6.0’s doubled speed to satisfy growing bandwidth and ultra-low-latency requirements.

- Hyperscale Data Centers – Early adopters using PCIe 6.0 to maintain scalability and efficiency, with stacked-die PCIe 6.0 SSDs easing storage bottlenecks in cloud-scale environments.

- AI/ML – High-bandwidth GPU and accelerator interfaces rely on PCIe 6.0 for rapid multi-processor data transfers essential to training and inference in large-scale AI and HPC systems.

- Quantum Computing – Even as it evolves, quantum tech needs fast, reliable data movement; PCIe 6.0 provides the speed and robust error correction to support future quantum workloads.

PCIe 6.0 Specification Features

- Delivers a raw data rate of 64.0 GT/s and achieves up to 256.0 GB/s bandwidth with a x16 lane configuration.

- Employs Pulse Amplitude Modulation with 4 levels (PAM4), leveraging proven PAM4 technology already established in the industry.

- Incorporates lightweight Forward Error Correction (FEC) and Cyclic Redundancy Check (CRC) to address the higher bit error rates associated with PAM4 signaling.

- Introduces FLIT (Flow Control Unit)–based encoding, which supports PAM4 modulation and works alongside FEC and CRC to deliver double the bandwidth efficiency.

- Uses an updated packet layout in FLIT mode, adding new functionality while simplifying data processing.

- Ensures full backward compatibility with all previous generations of PCIe technology.

What’s new in PCIe 6.0?

To achieve 64 GT/s, PCIe 6.0 introduces new features and innovations:

PAM4 Explained

With PCIe 6.0 making headlines, you’ve likely encountered the term “PAM4.” This modulation technique isn’t brand-new, but PCIe 6.0 marks the first time it’s built into the PCIe standard. So what is PAM4, and how does it power the next leap in PCIe performance?

1. PAM4 Signaling

To boost PCIe data transfer rates, there are two possible approaches: double the signal frequency or maintain the same frequency while using four voltage levels instead of two. PCIe 6.0 adopts the second method.

Earlier generations from PCIe 1.0 through 5.0 relied on Non-Return-to-Zero (NRZ) signaling, which uses two voltage levels—representing binary 1s and 0s, to convey 1 bit per unit interval (UI).

PCIe 6.0 retains the Gen 5 frequency but introduces four distinct voltage levels, 00, 01, 11, and 10 known as PAM4 (Pulse Amplitude Modulation, four-level).

This technique transmits 2 bits per UI, effectively doubling data throughput without increasing frequency.

Integrating four-level pulse amplitude modulation (PAM4) into PCIe 6.0 is a major advancement.

PCI-SIG adopted this upgrade to boost performance and prepare the interface for emerging technology markets.

PAM4 signaling, first added to the IEEE 802.3 Ethernet standard in 2017, has since gained wide adoption across high-speed networking systems.

![PCIe 6.0 – All You Need To Know About PCIe 6.0 [2025]](https://www.logic-fruit.com/wp-content/uploads/2023/08/PAM4.jpg)

2. Forward Error Correction (FEC)

There are always tradeoffs, and the transition to PAM4 signal encoding introduces a significantly higher Bit Error Rate (BER) vs. NRZ. This prompted the adoption of a Forward Error Correction (FEC) mechanism to mitigate the higher error rate.

Fortunately, the PCIe 6.0 FEC is sufficiently lightweight to have minimal impact on latency. It works in conjunction with strong CRC (Cyclic Redundancy Check) to keep Link Retry probability under 5×10-6. This new FEC feature targets an added latency under 2ns.

While PAM4 signaling is more susceptible to errors, channel loss is not affected compared to PCIe 5.0 due to the nature of the modulation technique, so the reach of PCIe 6.0 signals on a PCB will be the same as that of PCIe 5.0.

How Forward Error Correction (FEC) Improves PCIe 6.0 Reliability?

FEC provides real-time detection and correction of transmission errors, a necessity at PCIe 6.0’s ultra-high data rates.

By fixing errors on the fly, it cuts down on retransmissions, lowers latency, and keeps systems stable. This level of reliability is vital for demanding environments like data centers, AI processing, and high-speed network infrastructure.

3. FLIT Mode

In earlier PCIe versions, transactions used variable-length TLPs with fixed headers but varying data payloads, each protected by a 32-bit CRC.

With PCIe 6.0, PAM4 signaling introduces higher error rates, requiring FEC for reliability. Since FEC works best on fixed-size packets, PCIe 6.0 adopts FLIT (Flow Control Unit)–based encoding.

A FLIT in PCIe 6.0 has a fixed 256-byte size, including 236 bytes for TLP, 6 bytes for DLP, 8 bytes for CRC, and 6 bytes for FEC.

It eliminates overhead like sync headers and framing tokens, while the DLP also carries sequence numbers and control info for Ack/Nak and retry mechanisms.

FEC (Forward Error Correction) adds some latency and complexity, which grows with the number of symbols corrected. In PCIe 6.0, 6 FEC bytes are divided into 3 interleave groups (2 bytes each) to help prevent burst errors smaller than 3 bytes.

![PCIe 6.0 – All You Need To Know About PCIe 6.0 [2025]](https://www.logic-fruit.com/wp-content/uploads/2023/08/Untitled-1-scaled.jpg)

PCIe 6.0 encoding

Every 8 bits of data were converted into 10-bit characters before being delivered in PCIe versions 1.0 and 2.0, which results in a 20% overhead (you must transfer 10 bits of data even though you’re only attempting to send 8).

To communicate those same 2 extra bits, PCIe 3.0, 4.0, and 5.0 all employ 128b/130b encoding, which reduces the overhead to just 1.5%.

According to the PCI-SIG, PCIe 6.0 employs 1-bit to 1-bit (1b/1b) encoding, so the data encoded has no overhead. This means that if you want to send 8 bits over PCIe Gen 6, you only need to send 8 bits.

However, there is still some overhead in the form of additional FEC/CRC packets.

Designers should focus on three critical changes in PCIe 6.0 to ensure a smooth transition.

- Data rate doubled, increasing from 32 GT/s to 64 GT/s.

- Transition from NRZ to PAM4 signaling, introducing new error correction requirements.

- Shift from variable-length TLPs to fixed-size FLITs for more efficient data transport.

PCIe 6.0 vs. PCIe 5.0: Performance and Features

In this section, we will compare the performance and features of PCIe 6.0 with its predecessor, PCIe 5.0. Both of these standards represent significant advancements in high-speed data transfer, but there are notable differences between them. Let’s explore the critical aspects of PCIe 6.0 and how it compares to PCIe 5.0.

Data Rate and Bandwidth

- PCIe 5.0: PCIe 5.0 introduced a doubling of the data rate compared to PCIe 4.0, reaching a speed of 32 GT/s (Gigabytes transfers per second) per lane. This translates to approximately 4 GB/s (gigabytes per second) of raw bandwidth per lane.

- PCIe 6.0: PCIe 6.0 takes another leap in performance, doubling the data rate of PCIe 5.0. It offers a stunning speed of 64 GT/s per lane, providing approximately 8 GB/s of raw bandwidth per lane.

Lane configurations

- PCIe 5.0: PCIe 5.0 maintains the same lane configurations as its predecessor, supporting x1, x2, x4, x8, x16, and x32 configurations.

- PCIe 6.0: PCIe 6.0 also supports the same lane configurations as PCIe 5.0, allowing for x1, x2, x4, x8, x16, and x32 configurations.

Encoding and signaling

- PCIe 5.0: PCIe 5.0 introduced PAM4 (Pulse Amplitude Modulation 4-level) encoding, which enables more data to be transmitted per clock cycle compared to the previous NRZ (Non-Return-to-Zero) encoding used in PCIe 4.0.

- PCIe 6.0: PCIe 6.0 continues to use PAM4 encoding, but with additional enhancements to improve signal integrity and reduce errors, enabling reliable data transmission at higher speeds.

Forward Error Correction (FEC)

- PCIe 5.0: PCIe 5.0 introduced Reed-Solomon FEC (Forward Error Correction), which helps detect and correct transmission errors, improving the reliability of data transfer.

- PCIe 6.0: PCIe 6.0 enhances the FEC mechanism by adopting a more efficient low-density parity check (LDPC) FEC algorithm. LDPC provides superior error correction capabilities while reducing latency compared to Reed-Solomon FEC.

Power Efficiency

- PCIe 5.0: PCIe 5.0 introduced power-saving features, including L1 sub-states and L1.2 idle power management, which help reduce power consumption when the link is idle or operating at lower speeds.

- PCIe 6.0: PCIe 6.0 further enhances power efficiency by introducing new power management capabilities, allowing for deeper power-saving states and better overall energy efficiency.

Backward compatibility

- PCIe 5.0: PCIe 5.0 is backward compatible with PCIe 4.0, meaning PCIe 5.0 devices can be used in PCIe 4.0 slots, albeit at reduced speeds.

- PCIe 6.0: PCIe 6.0 is expected to maintain backward compatibility with previous versions, allowing PCIe 6.0 devices to work with older PCIe slots, albeit at lower speeds.

Overall, in terms of data rate, bandwidth, and raw throughput, PCIe 6.0 offers two times the performance of PCIe 5.0. Additionally, it includes improvements to power economy, error correction, and encoding. Due to these upgrades, PCIe 6.0 is well suited for demanding applications such as storage systems, high-performance computing, data centers, artificial intelligence, and machine learning.

Large datasets and demanding workloads can be handled with ease thanks to PCIe 6.0’s higher bandwidth and quicker data transmission speeds, which also enable faster and more efficient data processing.

Understanding PCIe 6.0 Optimizations

PCIe 6.0 brings significant design enhancements to deliver 64 GT/s per lane while preserving backward compatibility.

Beyond higher speed, the specification focuses on optimizing signaling, framing, and error handling to sustain efficiency at extreme data rates. Its development was guided by the following core optimization principles:

1. Reduce Loss: By Avoiding Unnecessary Encoding

Earlier PCIe generations used 8b/10b or 128b/130b encoding to maintain signal integrity, adding bandwidth overhead.

PCIe 6.0 eliminates this by adopting PAM4 signaling combined with Forward Error Correction (FEC), reducing data loss and freeing more bandwidth for actual data transfer.

2. Standardize Data Framing: Fixed-Size FLIT Mode

PCIe 6.0 replaces variable-sized packets with 256-byte fixed-size Flow Control Units (FLITs). This standardization simplifies protocol handling, reduces overhead, and enables more predictable, efficient data transfer at high speeds.

3. Remove Redundancy: Transmit Only Essential Data

In PCIe 6.0, control and metadata are integrated into the fixed FLIT structure, eliminating redundant transmissions.

With most data context inferred from the packet format, only essential signals are sent, reducing overhead, lowering latency, and enabling efficient high-speed operation

4. Streamline Link Management: Minimize Reconfiguration

Reconfiguration and link training are resource-intensive processes. PCIe 6.0 minimizes unnecessary renegotiation by reusing existing configurations, enabling faster system transitions and stable operation, even when scaling workloads or integrating with older PCIe generations.

Conclusion

In comparison to its predecessor, PCIe 5.0, PCIe 6.0 provides outstanding performance enhancements and cutting-edge capabilities. It is the next significant advancement in high-speed data transport.

For demanding applications including high-performance computing, data centers, AI, ML, and storage systems, PCIe 6.0 offers quicker and more efficient data processing capabilities with a two-fold increase in data throughput and enhanced bandwidth.

Data transmission reliability and energy economy are further increased with the introduction of PCIe 6.0 thanks to improvements in encoding, error correction, and power efficiency.

Large datasets, demanding workloads, and the processing needs of future technologies may all be handled without issue thanks to these developments.

While upgrading to PCIe 6.0 has many advantages, it’s necessary to take into account how well the existing infrastructure will work with the new standard and whether suitable hardware is readily available.

Since PCIe 6.0 is a relatively new standard, it might take some time before it is widely used while the market gets used to this most recent development.

Future PCIe standards promise to be quicker and more effective in terms of data transport. We should expect PCIe to advance further as technology develops, opening the door to improved connectivity and performance in the always-expanding digital environment.

In summary, PCIe 6.0 sets a new standard for high-speed data transfer, offering unparalleled performance, improved features, and increased efficiency.

Its capabilities make it a compelling choice for industries that demand high-bandwidth solutions, propelling innovation and enabling the next generation of computing experiences.

PCIe 7.0

Since its debut in 2002 at 2.5 GT/s, PCIe has evolved dramatically, reaching 64 GT/s with PCIe 6.0. Looking ahead, PCI-SIG has offered a preview of PCIe 7.0, with the specification released in June 2022.

While the standard is defined, the official release is scheduled for 2025, and compatible hardware will take additional time to enter the market.

About Logic Fruit Technologies

Logic Fruit Technologies is a leading provider of custom engineering solutions for high-performance embedded computing.

With expertise in PCIe technology, we offer a range of services including product development, testing and validation, and hardware design for various industries including automotive, aerospace, and medical devices.

Logic Fruit Technologies delivers customized solutions for high-performance embedded computing using PCIe technology. Our services include product development, testing, validation, and hardware design for various industries.

Logic Fruit Technologies has also been a member of PCI-SIG since 2017. As a member of PCI-SIG, Logic Fruit can collaborate with tier-1 semiconductor companies to develop effective design-to-test methodologies and decrease test costs for these advanced devices.

FPGA-Proven PCIe Gen 6 Controller IP

Logic Fruit’s PCIe Gen 6 Controller IP is FPGA-proven and already deployed by Tier 1 industry leaders, making it the first in the industry to deliver PCIe IP across multiple generations.

Built with future scalability in mind, this controller IP is:

- Optimized for both existing and emerging FPGA use cases, with a clear path to hardening on ASICs and SoCs.

- Ideal for large memory, compute-intensive, and high data rate applications that demand maximum performance and efficiency.

- Flexible, with porting support available and full access to previous-generation IPs for smooth migration and backward compatibility.

With unmatched expertise across the PCIe ecosystem, Logic Fruit ensures faster time-to-market and reliable performance for next-generation designs.

Download the datasheet today and see how our PCIe Gen 6 Controller IP can power your next innovation.

Frequently Asked Questions

What is the PCI Express (PCIe) 6.0 specification?

The most recent iteration of PCIe technology, the widely used and multipurpose PCI Express I/O specification, is PCI Express 6.0.

Data-intensive industries like as data centers, AI/ML, HPC, automotive, IoT, and military aerospace are supported by the PCIe 6.0 specification.

What are the initial target applications for the PCIe 6.0 architecture?

PCIe 6.0 technology’s first intended applications include servers, AI/ML, networking, and storage in data-intensive industries like industrial, automotive, military/aerospace, data centers, and HPC.

What are the new features in the PCIe 6.0 specification?

Low-latency Forward Error Correction (FEC), Flit (Flow Control Unit)-based encoding, and PAM4 (Pulse Amplitude Modulation with 4 levels) signaling are all introduced in the PCIe 6.0 specification.

Will PCIe 6.0 products be compatible with previous generations?

Yes, PCIe 6.0 products will work with all earlier PCI Express technology generations and remain backwards compatible.

Why does PCIe 6.0 specification utilize PAM4 signaling over NRZ signaling?

Data is transmitted using a multilayer signal modulation method called PAM4 (Pulse Amplitude Modulation with 4 Levels).

PAM4 employs four levels of signaling, whereas NRZ uses two. On a serial channel, it simultaneously transmits two bits of information.

The PCIe 6.0 specification uses PAM4 to achieve a data rate of 64.0 GT/s and a bidirectional bandwidth of up to 256.0 GB/s with an x16 arrangement.

How fast is PCIe 6.0 per lane?

PCIe 6.0 allows up to 8 GBps of bandwidth per lane with data rates of 64 GT/s. The inclusion of PAM4 (Pulse Amplitude Modulation with Four Levels), which doubles the data rate without necessitating a corresponding increase in clock speed, is the primary innovation in PCIe 6.0.

What is Forward Error Correction (FEC) and how is it utilized in the PCIe 6.0 specification?

The two main techniques for error correction in the PCIe 6.0 specification are powerful Cyclic Redundancy Check (CRC) and lightweight Forward Error Correction (FEC).

The PCIe 6.0 specification’s 64 GT/s data rate, made possible by PAM4 encoding, resulted in a bit error rate (BER) that was orders of magnitude higher than the 10-12 BER found in all previous generations.

By reducing the bit error rate, FEC and CRC enable the PCIe 6.0 specification to achieve unprecedented performance.

The higher BER anticipated in PAM4 (10-6 vs. 10-12 in NRZ) is supported by Flit Mode. Increased resilience in NRZ situations may result from this.

How fast is PCIe 6.0 x16?

With a maximum throughput of 256 GB/s for an x16 link and a raw data rate of 64 GT/s (gigatransfers per second), PCIe 6.0 doubles the data rate over PCIe 5.0.

How fast is PCIe Gen5 vs Gen6?

With a potential maximum bandwidth of 32 GT/s (giga transfers per second) per lane, Gen5 PCIe was released. This corresponds to about 64 GB/s for an x16 connection, or 4 GB/s per lane (in each direction).

This is further enhanced by PCIe Gen6, which doubles the bandwidth to 64 GT/s per lane.

What is the maximum speed of PCIe?

Depending on the generation and number of lanes utilized, PCIe (Peripheral Component Interconnect Express) maximum speed varies greatly.

For instance, PCIe 5.0 allows up to 128 GB/s in an x16 configuration (64 GB/s in one direction), but PCIe 6.0 doubles this to 8 GB/s per lane (128 GB/s in x16).

With each subsequent generation double the per-lane bandwidth of its predecessor, the actual speed that may be achieved depends on the particular PCIe version, the device and slot, and the number of lanes it utilizes.

![PCIe 6.0 – All You Need To Know About PCIe 6.0 [2025]](https://www.logic-fruit.com/wp-content/uploads/2025/09/PCIe-6.0-Thumbnail-1024x538-1.jpg)